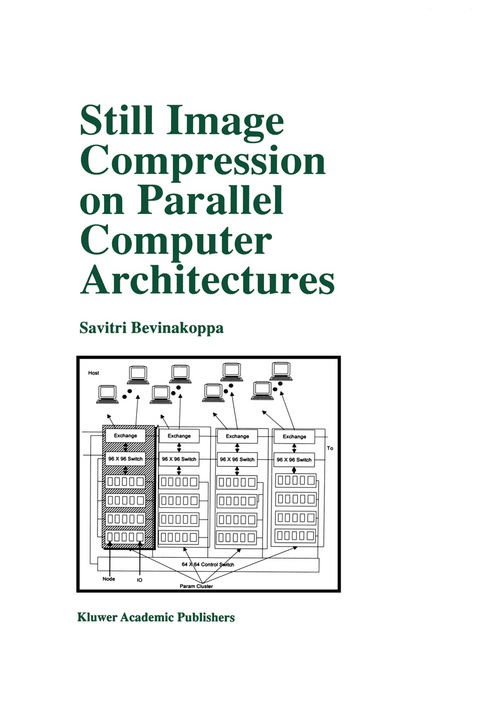

Still Image Compression on Parallel Computer Architectures

Springer (Verlag)

978-0-7923-8322-2 (ISBN)

A number of digital image compression algorithms have been developed and standardized. With the success of these algorithms, research effort is now directed towards improving implementation techniques. The Joint Photographic Experts Group (JPEG) and Motion Photographic Experts Group(MPEG) are international organizations which have developed digital image compression standards. Hardware (VLSI chips) which implement the JPEG image compression algorithm are available. Such hardware is specific to image compression only and cannot be used for other image processing applications. A flexible means of implementing digital image compression algorithms is still required. An obvious method of processing different imaging applications on general purpose hardware platforms is to develop software implementations.

JPEG uses an 8 × 8 block of image samples as the basic element for compression. These blocks are processed sequentially. There is always the possibility of having similar blocks in a given image. If similar blocks in an image are located, then repeatedcompression of these blocks is not necessary. By locating similar blocks in the image, the speed of compression can be increased and the size of the compressed image can be reduced. Based on this concept an enhancement to the JPEG algorithm is proposed, called Bock Comparator Technique (BCT).

Still Image Compression on Parallel Computer Architectures is designed for advanced students and practitioners of computer science. This comprehensive reference provides a foundation for understanding digital image compression techniques and parallel computer architectures.

1 Introduction.- 1.1 Introduction.- 1.2 Problem Statement.- 1.3 Literature Review.- 1.4 Research Objectives.- 1.5 Book Outline.- 2 Digital Image Compression Techniques.- 2.1 Introduction.- 2.2 Digital Image Compression Techniques.- 2.3 JPEG Standard.- 2.4 Block Comparator Enhancement to the JPEG Algorithm.- 2.5 Summary.- 3 Parallel Processing Plans for Digital Image Compression Techniques.- 3.1 Introduction.- 3.2 Parallel Computer Architectures.- 3.3 Parallel Processing Plans for Digital Image Compression Techniques.- 3.4 Implementation of Plans on Parallel Computer Architectures.- 3.5 Performance Measures.- 3.6 Summary.- 4 Implementation of Jpeg Algorithm on Parallel Computers.- 4.1 Introduction.- 4.2 Implementation of the JPEG Algorithm on the Mercury System.- 4.3 Implementation of the JPEG Algorithm on the Shiva System.- 4.4 Implementation of the JPEG Algorithm on the Param System.- 4.5 Performance Comparison of Parallel Computers.- 4.6 Summary.- 5 Simulation of Digital Image Compression Techniques.- 5.1 Introduction.- 5.2 Simulation Procedure.- 5.3 Simulation Results of Digital Image Compression Techniques.- 5.4 Performance Comparison of Parallel Architectures.- 5.5 Summary.- 6 Conclusions.- 6.1 Introduction.- 6.2 Block Comparator Technique Enhancement to the JPEG Algorithm.- 6.3 Implementation of the Digital Image Compression Algorithm.- 6.4 Simulation of Digital Image Compression.- 6.5 Directions for Future Research.- References.- Appendix A.

| Erscheint lt. Verlag | 30.11.1998 |

|---|---|

| Reihe/Serie | The Springer International Series in Engineering and Computer Science ; 475 |

| Zusatzinfo | XXV, 202 p. |

| Verlagsort | Dordrecht |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Informatik ► Grafik / Design ► Digitale Bildverarbeitung |

| Informatik ► Theorie / Studium ► Künstliche Intelligenz / Robotik | |

| Technik | |

| ISBN-10 | 0-7923-8322-2 / 0792383222 |

| ISBN-13 | 978-0-7923-8322-2 / 9780792383222 |

| Zustand | Neuware |

| Informationen gemäß Produktsicherheitsverordnung (GPSR) | |

| Haben Sie eine Frage zum Produkt? |

aus dem Bereich