Simultaneous Switching Noise of CMOS Devices and Systems

Springer (Verlag)

978-0-7923-9400-6 (ISBN)

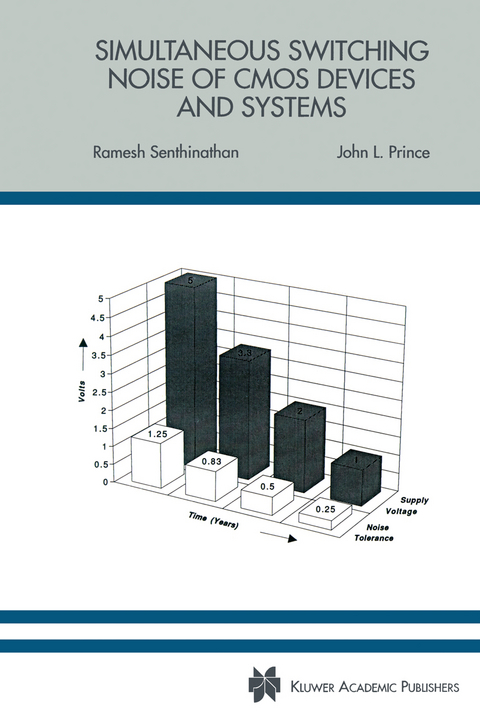

This monograph presents our recent research on Simultaneous Switching Noise (SSN) and related issues for CMOS based systems. Although some SSN related work was previously reported in the literature, it were mainly for Emitter Coupled Logic (ECL) gates using Bipolar Junction Transistors (BJTs). This present work covers in-depth analysis on estimating SSN and its impact for CMOS based devices and systems. At present semiconductor industries are moving towards scaled CMOS devices and reduced supply voltage. SSN together with coupled noise may limit the packing density, and thereby the frequency of operation of packaged systems. Our goal is to provide efficient and yet reliable methodologies and algorithms to estimate the overall noise containment in single chip and multi-chip package assemblies. We hope that the techniques and results described in this book will be useful as guides for design, package, and system engineers and academia working in this area. Through this monograph, we hope that we have shown the necessity of interactions that are essential between chip design, system design and package design engineers to design and manufacture optimal packaged systems. Work reported in this monograph was partially supported by the grant from Semiconductor Research Corporation (SRC Contract No. 92-MP-086).

1 — Introduction.- 1.1 Background.- 1.2 Introduction.- 2 — Packaged/Scaled CMOS Devices.- 2.1 Introduction.- 2.2 Interconnect Scaling.- 2.3 Delays with Driver/Interconnect Scaling.- 2.4 Summary.- 3 — Methods of Calculating Simultaneous Switching Noise.- 3.1 Introduction.- 3.2 Theory and Modeling.- 3.3 Ground Noise and Vss Pad-Pin Connection Calculation..- 3.4 Results.- 3.5 Behavior of Simultaneous Switching Noise with Scaling..- 3.6 Summary.- 4 — Power Distribution Inductance Modeling.- 4.1 Introduction.- 4.2 Mathematical Formulation of UALGRL.- 4.3 Effective Inductance “Lvss” Modeling.- 4.4 Reference Plane Inductance Network Calculation..- 4.5 Results.- 4.6 Summary.- 5 — Signal Conductors over a Perforated Reference Plane.- 5.1 Introduction.- 5.2 Impact of Reference Plane Openings for Stripline Geometries.- 5.3 Connector Characterization Using S—Parameter Measurement Techniques.- 5.4 Modeling Using Two Dimensional (TEM) Approximation.- 5.5 Three—Dimensional Modeling Technique.- 5.6 Comparison Between Measurement and Simulations..- 5.7 Full—Wave Analysis of a Periodically Perforated Structure.- 5.8 Summary.- 6 — Dynamic Noise Immunity, and Skewing/Damping SSN Waveform.- 6.1 Introduction.- 6.2 Driver Switching Noise and Receiver Noise Immunity.- 6.3 Effects of Skewing Output Drivers.- 6.4 Trade—offs in Using Damping Resistors.- 6.5 Summary.- 7 — Application Specific Output Drivers to Reduce SSN.- 7.1 Introduction.- 7.2 CMOS Output Driver Switching Current Components.- 7.3 Current Controlled Output Drivers.- 7.4 Controlled Slew Rate Output Drivers.- 7.5 Summary.- 8 — SSN Simulator Architecture.- 8.1 Introduction.- 8.2 SSNS Architecture.- 8.3 “Less” Modeling for MCM Vss Connections.- 8.4 Simultaneous Switching Noise Calculation for CMOS MCM123 8.5 Summary.- 9 — Signal Conductors over a Noisy Reference Plane.- 9.1 Introduction and Motivation.- 9.2 Equivalent Electrical Circuit Model Formulation.- 9.3 Calculation of Lumped Circuit Elements.- 9.4 Transient Response Simulations.- 9.5 Impact of Vss Package—Pin Placement on Noise Modeling.- 9.6 Summary.- 10 — Conclusions.- 11 — Discussion and Future Work.- 11.1 BiCMOS Outputs Simultaneous Switching Noise...- 11.2 Use of Substrate-Taps to Reduce SSN.- 11.3 SSNS Architecture Improvement.- Appendix A.- Appendix B.- Appendix C.- Appendix D.- Appendix E.- References.- About the Authors.

| Erscheint lt. Verlag | 30.11.1993 |

|---|---|

| Reihe/Serie | The Springer International Series in Engineering and Computer Science ; 249 |

| Zusatzinfo | XXI, 205 p. |

| Verlagsort | Dordrecht |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Technik ► Elektrotechnik / Energietechnik |

| ISBN-10 | 0-7923-9400-3 / 0792394003 |

| ISBN-13 | 978-0-7923-9400-6 / 9780792394006 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

aus dem Bereich