Moderne Prozessorarchitekturen

Springer Berlin (Verlag)

978-3-540-24390-8 (ISBN)

Das Buch behandelt die in modernen Hochleistungsprozessoren zum Einsatz kommenden Techniken. Nach einer einführenden Beschreibung von Programmiermodellen werden zunächst skalare Prozessoren, die Mikroprogrammierung und die Fließbandverarbeitung diskutiert.

Die in operationsparallel arbeitenden Prozessoren angewandten Prinzipien kommen zur Sprache. Dabei werden die Multimedia-Einheiten (SIMD-Einheiten), Feldrechner, Vektorrechner, Signalprozessoren, VLIW-Prozessoren und Prozessoren mit kontrollflussgesteuertem Datenfluss erörtert - zum Teil auch unter Einbeziehung der bei diesen Verfahren bedeutsamen Übersetzerbautechniken. Im Zusammenhang mit den ebenfalls behandelten superskalaren Prozessoren werden die gängigen Verfahren zur Operationsparallelisierung, zum Reordering von Befehlen, zur Datenflussspekulation und zur Kontrollflussspekulation beschrieben. Zum Abschluss beschäftigt sich das Buch mit Techniken zum Aufbau von im Hardware/Software-Codedesign arbeitenden Prozessoren.

Die einzelnen Kapitel sind so aufgebaut, dass zunächst die Idee eines Prinzips sowie eine Umsetzung beschrieben wird. Anschließend werden Schwachstellen herausgearbeitet und darauf aufbauend verbesserte Umsetzungen präsentiert.

Das Buch vermittelt nicht nur die Ideen der im Prozessorbau zum Einsatz kommenden Verfahren, sondern insbesondere die für eine Umsetzung erforderlichen Details, die vielfach bis hinab zur Registertransferschaltung führen. Es enthält zahlreiche Bilder bzw. Tabellen und Beispiele.

Matthias Menge studierte Elektrotechnik an der Technischen Universität Berlin. Im Anschluss daran war er als Wissenschaftlicher Mitarbeiter, nach seiner Promotion als Wissenschaftlicher Assistent an der Technischen Universität Berlin im Fachgebiet "Rechnerorganisation und Schaltwerksentwurf" tätig. Schwerpunkt seiner wissenschaftlichen Arbeiten ist der Prozessorbau, den er seit 1990 auch in Lehrveranstaltungen an Studierende vermittelt. Darüber hinaus war er langjährig freiberuflich tätig.

Programmiermodell.- Skalare Prozessoren.- Operationsparallel arbeitende Prozessoren.- Prozessorbau im Hardware-Software-Codesign.

| Erscheint lt. Verlag | 9.3.2005 |

|---|---|

| Zusatzinfo | XVI, 384 S. |

| Verlagsort | Berlin |

| Sprache | deutsch |

| Maße | 155 x 235 mm |

| Gewicht | 595 g |

| Themenwelt | Mathematik / Informatik ► Informatik ► Theorie / Studium |

| Informatik ► Weitere Themen ► Hardware | |

| Technik ► Elektrotechnik / Energietechnik | |

| Schlagworte | Elektrotechnik • Hardcover, Softcover / Informatik, EDV/Informatik • Hardware • Hardware-/Software-Codesign • HC/Informatik, EDV/Informatik • HC/Technik/Maschinenbau, Fertigungstechnik • Hochleistungsprozessor • Leistung • Mikroprogrammierung • Multimedia • Multimedia-Einheiten • operationparallel arbeitende Prozessoren • Programmierung • Prozessor • Prozessorarchitektur • Schaltung • Signal • Signalprozessor • Software • Tabellen |

| ISBN-10 | 3-540-24390-9 / 3540243909 |

| ISBN-13 | 978-3-540-24390-8 / 9783540243908 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

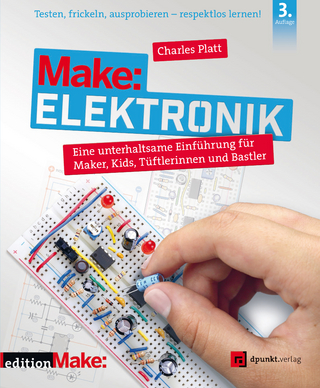

aus dem Bereich