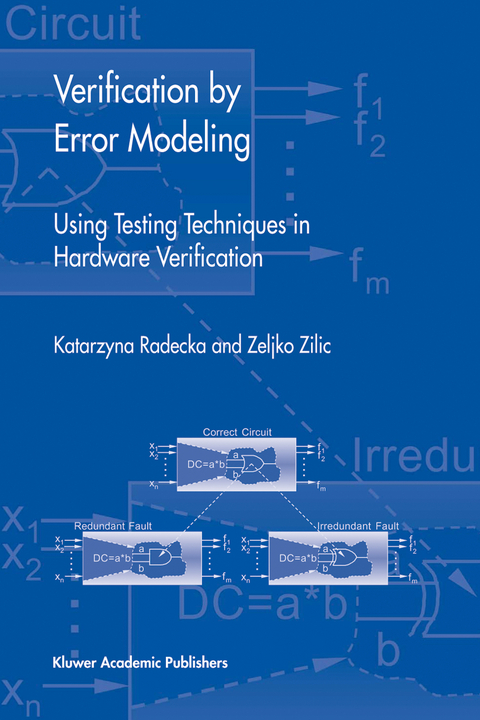

Verification by Error Modeling

Using Testing Techniques in Hardware Verification

Seiten

2003

Springer-Verlag New York Inc.

978-1-4020-7652-7 (ISBN)

Springer-Verlag New York Inc.

978-1-4020-7652-7 (ISBN)

Although there are no widely adhered standards for a design flow, most companies have their own established practices, which they follow closely for in-house design processes. In practice, initial phases of preparing a design specification are susceptible to potential errors, as it is very difficult to grasp all the details in a complex design.

1. DESIGN FLOW Integrated circuit (IC) complexity is steadily increasing. ICs incorporating hundreds of millions of transistors, mega-bit memories, complicated pipelined structures, etc., are now in high demand. For example, Intel Itanium II processor contains more than 200 million transistors, including a 3 MB third level cache. A billion transistor IC was said to be “imminently doable” by Intel fellow J. Crawford at Microprocessor Forum in October 2002 [40]. Obviously, designing such complex circuits poses real challenges to engineers. Certainly, no relief comes from the competitive marketplace, with increasing demands for a very narrow window of time (time-to-market) in engineering a ready product. Therefore, a systematic and well-structured approach to designing ICs is a must. Although there are no widely adhered standards for a design flow, most companies have their own established practices, which they follow closely for in-house design processes. In general, however, a typical product cycle includes few milestones. An idea for a new product starts usually from an - depth market analysis of customer needs. Once a window of opportunity is found, product requirements are carefully specified. Ideally, these parameters would not change during the design process. In practice, initial phases of preparing a design specification are susceptible to potential errors, as it is very difficult to grasp all the details in a complex design.

1. DESIGN FLOW Integrated circuit (IC) complexity is steadily increasing. ICs incorporating hundreds of millions of transistors, mega-bit memories, complicated pipelined structures, etc., are now in high demand. For example, Intel Itanium II processor contains more than 200 million transistors, including a 3 MB third level cache. A billion transistor IC was said to be “imminently doable” by Intel fellow J. Crawford at Microprocessor Forum in October 2002 [40]. Obviously, designing such complex circuits poses real challenges to engineers. Certainly, no relief comes from the competitive marketplace, with increasing demands for a very narrow window of time (time-to-market) in engineering a ready product. Therefore, a systematic and well-structured approach to designing ICs is a must. Although there are no widely adhered standards for a design flow, most companies have their own established practices, which they follow closely for in-house design processes. In general, however, a typical product cycle includes few milestones. An idea for a new product starts usually from an - depth market analysis of customer needs. Once a window of opportunity is found, product requirements are carefully specified. Ideally, these parameters would not change during the design process. In practice, initial phases of preparing a design specification are susceptible to potential errors, as it is very difficult to grasp all the details in a complex design.

Boolean Function Representations.- Don’t Cares and Their Calculation.- Testing.- Design Error Models.- Design Verification by At.- Identifying Redundant Gate and Wire Replacements.- Conclusions and Future Work.

| Erscheint lt. Verlag | 30.11.2003 |

|---|---|

| Reihe/Serie | Frontiers in Electronic Testing ; 25 |

| Zusatzinfo | XV, 216 p. |

| Verlagsort | New York, NY |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Informatik ► Theorie / Studium ► Künstliche Intelligenz / Robotik |

| Technik ► Elektrotechnik / Energietechnik | |

| Technik ► Maschinenbau | |

| ISBN-10 | 1-4020-7652-5 / 1402076525 |

| ISBN-13 | 978-1-4020-7652-7 / 9781402076527 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

Mehr entdecken

aus dem Bereich

aus dem Bereich

was sie kann & was uns erwartet

Buch | Softcover (2023)

C.H.Beck (Verlag)

18,00 €

von absurd bis tödlich: Die Tücken der künstlichen Intelligenz

Buch | Softcover (2023)

Heyne (Verlag)

20,00 €

dem Menschen überlegen – wie KI uns rettet und bedroht

Buch | Hardcover (2023)

Droemer (Verlag)

24,00 €