Test Resource Partitioning for System-on-a-Chip

Seiten

2012

|

Softcover reprint of the original 1st ed. 2002

Springer-Verlag New York Inc.

978-1-4613-5400-0 (ISBN)

Springer-Verlag New York Inc.

978-1-4613-5400-0 (ISBN)

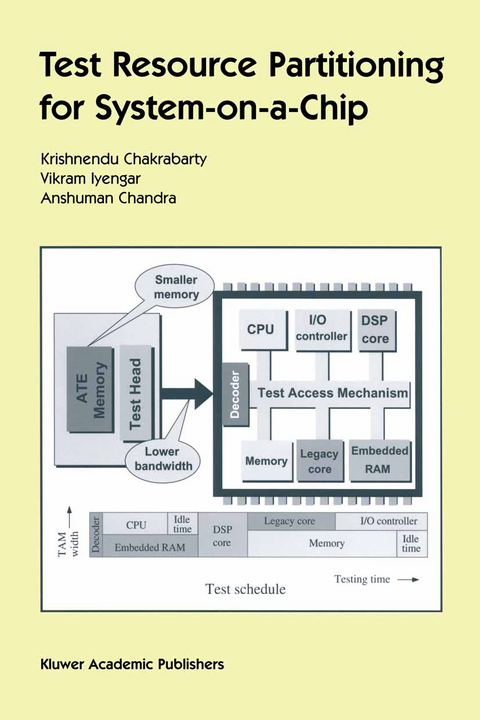

Test Resource Partitioning for System-on-a-Chip is about test resource partitioning and optimization techniques for plug-and-play system-on-a-chip (SOC) test automation. Plug-and-play refers to the paradigm in which core-to-core interfaces as well as core-to-SOC logic interfaces are standardized, such that cores can be easily plugged into "virtual sockets" on the SOC design, and core tests can be plugged into the SOC during test without substantial effort on the part of the system integrator. The goal of the book is to position test resource partitioning in the context of SOC test automation, as well as to generate interest and motivate research on this important topic.

SOC integrated circuits composed of embedded cores are now commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols.

Test Resource Partitioning for System-on-a-Chip responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume.

Test Resource Partitioning for System-on-a-Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.

SOC integrated circuits composed of embedded cores are now commonplace. Nevertheless, There remain several roadblocks to rapid and efficient system integration. Test development is seen as a major bottleneck in SOC design, and test challenges are a major contributor to the widening gap between design capability and manufacturing capacity. Testing SOCs is especially challenging in the absence of standardized test structures, test automation tools, and test protocols.

Test Resource Partitioning for System-on-a-Chip responds to a pressing need for a structured methodology for SOC test automation. It presents new techniques for the partitioning and optimization of the three major SOC test resources: test hardware, testing time and test data volume.

Test Resource Partitioning for System-on-a-Chip paves the way for a powerful integrated framework to automate the test flow for a large number of cores in an SOC in a plug-and-play fashion. The framework presented allows the system integrator to reduce test cost and meet short time-to-market requirements.

1. Test Resource Partitioning.- 2. Test Access Mechanism Optimization.- 3. Improved Test Bus Partitioning.- 4. Test Wrapper And TAM Co-Optimization.- 5. Test Scheduling.- 6. Precedence, Preemption, And Power Constraints.- 7. Test Data Compression Using Golomb Codes.- 8. Frequency-Directed Run-Length (FDR) Codes.- 9. TRP for Low-Power Scan Testing.- 10. Conclusion.- References.

| Reihe/Serie | Frontiers in Electronic Testing ; 20 |

|---|---|

| Zusatzinfo | XII, 232 p. |

| Verlagsort | New York, NY |

| Sprache | englisch |

| Maße | 155 x 235 mm |

| Themenwelt | Informatik ► Weitere Themen ► CAD-Programme |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 1-4613-5400-5 / 1461354005 |

| ISBN-13 | 978-1-4613-5400-0 / 9781461354000 |

| Zustand | Neuware |

| Haben Sie eine Frage zum Produkt? |

Mehr entdecken

aus dem Bereich

aus dem Bereich

Buch | Softcover (2023)

Beuth (Verlag)

99,00 €

Einführung in die Geometrische Produktspezifikation

Buch | Softcover (2023)

Europa-Lehrmittel (Verlag)

20,70 €