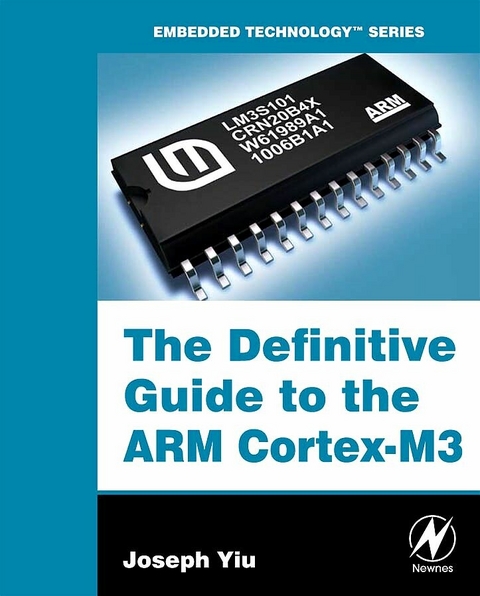

Definitive Guide to the ARM Cortex-M3 (eBook)

384 Seiten

Elsevier Science (Verlag)

978-0-08-055143-2 (ISBN)

Whole chapters are dedicated to:

Debugging using the new CoreSight technology

Migrating effectively from the ARM7

The Memory Protection Unit

Interfaces, Exceptions,Interrupts

...and much more!

*The only available guide to programming and using the groundbreaking ARM Cortex-M3 processor

*Easy-to-understand examples, diagrams, quick reference appendices, full instruction and Thumb-2 instruction sets are all included

*The author, an ARM engineer on the M3 development team, teaches end users how to start from the ground up with the M3, and how to migrate from the ARM7

This user's guide does far more than simply outline the ARM Cortex-M3 CPU features; it explains step-by-step how to program and implement the processor in real-world designs. It teaches readers how to utilize the complete and thumb instruction sets in order to obtain the best functionality, efficiency, and reuseability. The author, an ARM engineer who helped develop the core, provides many examples and diagrams that aid understanding. Quick reference appendices make locating specific details a snap! Whole chapters are dedicated to: Debugging using the new CoreSight technologyMigrating effectively from the ARM7 The Memory Protection Unit Interfaces, Exceptions,Interrupts ...and much more!*The only available guide to programming and using the groundbreaking ARM Cortex-M3 processor *Easy-to-understand examples, diagrams, quick reference appendices, full instruction and Thumb-2 instruction sets are all included *The author, an ARM engineer on the M3 development team, teaches end users how to start from the ground up with the M3, and how to migrate from the ARM7

Front Cover 1

The Definitive Guide to the ARM Cortex-M3 4

Copyright Page 5

Table of Contents 6

Foreword 14

Preface 15

Acknowledgments 16

Terms and Abbreviations 17

Conventions 19

References 20

Chapter 1 – Introduction 22

What Is the ARM Cortex-M3 Processor? 22

Background of ARM and ARM Architecture 24

A Brief History 24

Architecture Versions 25

Processor Naming 27

Instruction Set Development 29

The Thumb-2 Instruction Set Architecture (ISA) 30

Cortex-M3 Processor Applications 31

Organization of This Book 32

Further Readings 32

Chapter 2 – Overview of the Cortex-M3 34

Fundamentals 34

Registers 35

R0 to R12: General-Purpose Registers 35

R13: Stack Pointers 35

R14: The Link Register 36

R15: The Program Counter 36

Special Registers 36

Operation Modes 37

The Built-In Nested Vectored Interrupt Controller 38

Nested Interrupt Support 39

Vectored Interrupt Support 39

Dynamic Priority Changes Support 39

Reduction of Interrupt Latency 39

Interrupt Masking 39

The Memory Map 40

The Bus Interface 41

The Memory Protection Unit 41

The Instruction Set 41

Interrupts and Exceptions 43

Debugging Support 45

Characteristics Summary 46

High Performance 46

Advanced Interrupt-Handling Features 46

Low Power Consumption 47

System Features 47

Debug Supports 47

Chapter 3 – Cortex-M3 Basics 50

Registers 50

General-Purpose Registers R0–R7 50

General-Purpose Registers R8–R12 50

Stack Pointer R13 51

Link Register R14 53

Program Counter R15 54

Special Registers 54

Program Status Registers (PSRs) 54

PRIMASK, FAULTMASK, and BASEPRI Registers 56

The Control Register 57

Operation Mode 58

Exceptions and Interrupts 60

Vector Tables 61

Stack Memory Operations 62

Basic Operations of the Stack 62

Cortex-M3 Stack Implementation 63

The Two-Stack Model in the Cortex-M3 64

Reset Sequence 65

Chapter 4 – Instruction Sets 68

Assembly Basics 68

Assembler Language: Basic Syntax 68

Assembler Language: Use of Suffixes 69

Assembler Language: Unified Assembler Language 70

Instruction List 71

Unsupported Instructions 76

Instruction Descriptions 78

Assembler Language: Moving Data 78

LDR and ADR Pseudo Instructions 81

Assembler Language: Processing Data 82

Assembler Language: Call and Unconditional Branch 87

Assembler Language: Decisions and Conditional Branches 88

Assembler Language: Combined Compare and Conditional Branch 91

Assembler Language: Conditional Branches Using IT Instructions 92

Assembler Language: Instruction Barrier and Memory Barrier Instructions 93

Assembly Language: Saturation Operations 94

Several Useful Instructions in the Cortex-M3 96

MSR and MRS 96

IF-THEN 97

CBZ and CBNZ 98

SDIV and UDIV 99

REV, REVH, and REVSH 99

RBIT 99

SXTB, SXTH, UXTB, and UXTH 100

BFC and BFI 100

UBFX and SBFX 100

LDRD and STRD 101

TBB and TBH 101

Chapter 5 – Memory Systems 104

Memory System Features Overview 104

Memory Maps 104

Memory Access Attributes 107

Default Memory Access Permissions 109

Bit-Band Operations 109

Advantages of Bit-Band Operations 113

Bit-Band Operation of Different Data Sizes 116

Bit-Band Operations in C Programs 116

Unaligned Transfers 117

Exclusive Accesses 119

Endian Mode 121

Chapter 6 – Cortex-M3 Implementation Overview 124

The Pipeline 124

A Detailed Block Diagram 126

Bus Interfaces on the Cortex-M3 129

The I-Code Bus 129

The D-Code Bus 129

The System Bus 130

The External Private Peripheral Bus 130

The Debug Access Port Bus 130

Other Interfaces on the Cortex-M3 130

The External Private Peripheral Bus 130

Typical Connections 132

Reset Signals 133

Chapter 7 – Exceptions 136

Exception Types 136

Definitions of Priority 138

Vector Tables 144

Interrupt Inputs and Pending Behavior 145

Fault Exceptions 148

Bus Faults 148

Memory Management Faults 150

Usage Faults 151

Hard Faults 153

Dealing with Faults 153

SVC and PendSV 154

Chapter 8 – The NVIC and Interrupt Control 158

NVIC Overview 158

The Basic Interrupt Configuration 159

Interrupt Enable and Clear Enable 159

Interrupt Pending and Clear Pending 159

Priority Levels 161

Active Status 162

PRIMASK and FAULTMASK Special Registers 162

The BASEPRI Special Register 163

Configuration Registers for Other Exceptions 164

Example Procedures of Setting Up an Interrupt 165

Software Interrupts 167

The SYSTICK Timer 168

Chapter 9 – Interrupt Behavior 170

Interrupt/Exception Sequences 170

Stacking 170

Vector Fetches 171

Register Updates 172

Exception Exits 172

Nested Interrupts 173

Tail-Chaining Interrupts 173

Late Arrivals 174

More on the Exception Return Value 174

Interrupt Latency 175

Faults Related to Interrupts 177

Stacking 177

Unstacking 178

Vector Fetches 178

Invalid Returns 178

Chapter 10 – Cortex-M3 Programming 180

Overview 180

Using Assembly 180

Using C 181

The Interface Between Assembly and C 182

A Typical Development Flow 183

The First Step 183

Producing Outputs 185

The "Hello World" Example 186

Using Data Memory 190

Using Exclusive Access for Semaphores 191

Using Bit-Band for Semaphores 193

Working with Bit Field Extract and Table Branch 194

Chapter 11 – Exceptions Programming 196

Using Interrupts 196

Stack setup 196

Vector Table Setup 197

Interrupt Priority Setup 198

Enable the Interrupt 199

Exception/Interrupt Handlers 200

Software Interrupts 201

Example with Exception Handlers 202

Using SVC 205

SVC Example: Use for Output Functions 207

Using SVC with C 210

Chapter 12 – Advanced Programming Features and System Behavior 214

Running a System with Two Separate Stacks 214

Double-Word Stack Alignment 217

Nonbase Thread Enable 218

Performance Considerations 221

Lockup Situations 222

What Happens During Lockup? 222

Avoiding Lockup 223

Chapter 13 – The Memory Protection Unit 226

Overview 226

MPU Registers 227

Setting Up the MPU 232

Typical Setup 238

Example Use of the Subregion Disable 238

Chapter 14 – Other Cortex-M3 Features 244

The SYSTICK Timer 244

Power Management 248

Multiprocessor Communication 250

Self-Reset Control 252

Chapter 15 – Debug Architecture 254

Debugging Features Overview 254

CoreSight Overview 255

Processor Debugging Interface 255

The Debug Host Interface 256

DP Module, AP Module, and DAP 256

Trace Interface 257

CoreSight Characteristics 258

Debug Modes 260

Debugging Events 262

Breakpoint in the Cortex-M3 264

Accessing Register Content in Debug 265

Other Core Debugging Features 266

Chapter 16 – Debugging Components 268

Introduction 268

The Trace System in the Cortex-M3 268

Trace Components: Data Watchpoint and Trace 269

Trace Components: Instrumentation Trace Macrocell 271

Software Trace with the ITM 272

Hardware Trace with ITM and DWT 272

ITM Timestamp 272

Trace Components: Embedded Trace Macrocell 273

Trace Components: Trace Port Interface Unit 274

The Flash Patch and Breakpoint Unit 274

The AHB Access Port 277

ROM Table 278

Chapter 17 – Getting Started with Cortex-M3 Development 280

Choosing a Cortex-M3 Product 280

Differences Between Cortex-M3 Revision 0 and Revision 1 281

Revision 1 Change: Moving from JTAG-DP to SWJ-DP 282

Development Tools 283

C Compiler 283

Embedded Operating System Support 284

Chapter 18 – Porting Applications from the ARM7 to the Cortex-M3 286

Overview 286

System Characteristics 287

Memory Map 287

Interrupts 287

MPU 288

System Control 288

Operation Modes 288

Assembly Language Files 289

Thumb State 289

ARM State 290

C Program Files 292

Precompiled Object Files 292

Optimization 292

Chapter 19 – Starting Cortex-M3 Development Using the GNU Tool Chain 294

Background 294

Getting the GNU Tool Chain 294

Development Flow 295

Examples 296

Example 1: The First Program 296

Example 2: Linking Multiple Files 298

Example 3: A Simple "Hello World" Program 299

Example 4: Data in RAM 301

Example 5: C Only, Without Assembly File 302

Example 6: C Only, with Standard C Startup Code 306

Accessing Special Registers 308

Using Unsupported Instructions 308

Inline Assembler in the GNU C Compiler 308

Chapter 20 – Getting Started with the KEIL RealView Microcontroller Development Kit 310

Overview 310

Getting Started with & #956

Outputting the "Hello World" Message Via UART 316

Testing the Software 319

Using the Debugger 321

The Instruction Set Simulator 324

Modifying the Vector Table 326

Stopwatch Example with Interrupts 327

Appendix A – Cortex-M3 Instructions Summary 336

Supported 16-Bit Thumb Instructions 336

Supported 32-Bit Thumb-2 Instructions 340

Appendix B – 16-Bit Thumb Instructions and Architecture Versions 350

Appendix C – Cortex-M3 Exceptions Quick Reference 352

Exception Types and Enables 352

Stack Contents After Exception Stacking 353

Appendix D – NVIC Registers Quick Reference 354

Appendix E – Cortex-M3 Troubleshooting Guide 368

Overview 368

Developing Fault Handlers 369

Report Fault Status Registers 370

Report Stacked PC 370

Read Fault Address Register 371

Clear Fault Status Bits 371

Others 371

Understanding the Cause of the Fault 372

Other Possible Problems 375

Index 376

A 376

B 376

C 377

D 377

E 377

F 378

H 378

I 378

L 378

M 378

N 378

P 379

Q 379

R 379

S 379

T 380

U 380

V 380

W 380

X 380

| Erscheint lt. Verlag | 8.4.2011 |

|---|---|

| Sprache | englisch |

| Themenwelt | Kunst / Musik / Theater ► Design / Innenarchitektur / Mode |

| Technik ► Elektrotechnik / Energietechnik | |

| ISBN-10 | 0-08-055143-2 / 0080551432 |

| ISBN-13 | 978-0-08-055143-2 / 9780080551432 |

| Haben Sie eine Frage zum Produkt? |

Größe: 3,7 MB

Kopierschutz: Adobe-DRM

Adobe-DRM ist ein Kopierschutz, der das eBook vor Mißbrauch schützen soll. Dabei wird das eBook bereits beim Download auf Ihre persönliche Adobe-ID autorisiert. Lesen können Sie das eBook dann nur auf den Geräten, welche ebenfalls auf Ihre Adobe-ID registriert sind.

Details zum Adobe-DRM

Dateiformat: PDF (Portable Document Format)

Mit einem festen Seitenlayout eignet sich die PDF besonders für Fachbücher mit Spalten, Tabellen und Abbildungen. Eine PDF kann auf fast allen Geräten angezeigt werden, ist aber für kleine Displays (Smartphone, eReader) nur eingeschränkt geeignet.

Systemvoraussetzungen:

PC/Mac: Mit einem PC oder Mac können Sie dieses eBook lesen. Sie benötigen eine

eReader: Dieses eBook kann mit (fast) allen eBook-Readern gelesen werden. Mit dem amazon-Kindle ist es aber nicht kompatibel.

Smartphone/Tablet: Egal ob Apple oder Android, dieses eBook können Sie lesen. Sie benötigen eine

Geräteliste und zusätzliche Hinweise

Buying eBooks from abroad

For tax law reasons we can sell eBooks just within Germany and Switzerland. Regrettably we cannot fulfill eBook-orders from other countries.

aus dem Bereich